Quick Start : Designing with AMD Versal™ Adaptive SoC (French Language) 9h - 17h CET

(ref.A_QSTART)

1 day - 7 hours

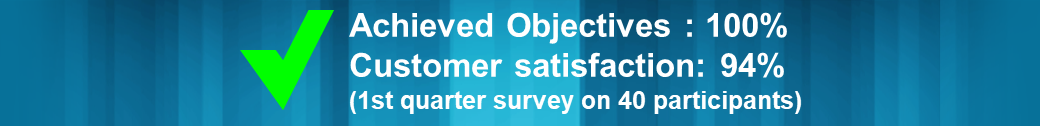

Objectives

- During the event, you'll be introduced to the new AMD Versal™ platform. Explore the heterogeneous Versal™ adaptive SoC architecture containing programmable network-on-chip (NoC) and AI engines, and learn how to use different design tool flows targeting Versal devices.

Prerequisites

- Comfort with the C/C++ programming language

- Vitis™ IDE software development flow

- Hardware development flow with the Vivado™ Design Suite

- Basic knowledge of UltraScale™/UltraScale+™ FPGAs and Zynq™ UltraScale+ MPSoCs

Concerned public

- Technicians and Engineers in Digital Electronics

- All our training courses are given at a distance and are accessible to people with reduced mobility.

- Our partner AGEFIPH accompanies us to implement the necessary adaptations related to your disability.

Notes

- Release date: 01/02/202420/07/2023

Chapters

Architecture Overview {Lecture}

Design Tool Flow {Lecture, Demo}

Embedded Software Development {Lecture, Demo}

NoC Introduction and Concepts {Lecture, Demo}

AI Engine {Lecture, Demo}

Teaching Methods

Support

- Authorized Trainer Provider AMD : Engineer Electronics and Telecommunications ENSIL

- Expert AMD FPGA - Language VHDL/Verilog - RTL Design

- Expert AMD SoC & MPSoC - Language C/C++ - System Design

- Expert DSP & AMD RFSoC – HLS - Matlab - Design DSP RF

- Expert AMD Versal – AI Engines – Heteregenous System Architect

PC Recommended

- Software Configuration :

- Hardware configuration:

- Recent computer (i5 or i7)

- OS Linux 64-bits (Windows 10 compatible)

- At least 16GB RAM

- Recommended display resolution 1920x1080